1.1 什么是38译码器

38译码器是一种常见的数字集成电路。它的名字来源于功能特性:3个输入引脚对应8个输出引脚。想象一下它就像一个高效的信号分发员,能够将3位二进制代码转换成8个独立的输出信号。

这类器件在数字系统中扮演着重要角色。当我们需要从多个设备中选择特定对象时,38译码器就能派上用场。它通过简单的输入组合,精确激活对应的输出线路。这种一对多的映射关系,让电路设计变得更加简洁高效。

我记得第一次在实验室接触38译码器时,惊讶于它的巧妙设计。仅仅三个输入就能控制八个不同的设备,这种效率提升确实令人印象深刻。

1.2 38译码器的基本结构

38译码器的内部构造相当精妙。核心部分包含三个主要模块:输入缓冲电路、译码逻辑阵列和输出驱动单元。

输入缓冲电路负责处理三个输入信号,确保信号的稳定性和完整性。译码逻辑阵列由多个与门和非门组成,这是实现3-8转换的关键所在。输出驱动单元则负责增强信号驱动能力,确保输出信号能够有效控制后续电路。

整个结构采用对称设计,输出引脚通常按顺序排列。这种规整的布局不仅便于理解,也简化了电路板布线。内部逻辑门的连接方式经过优化,确保信号传输延迟最小化。

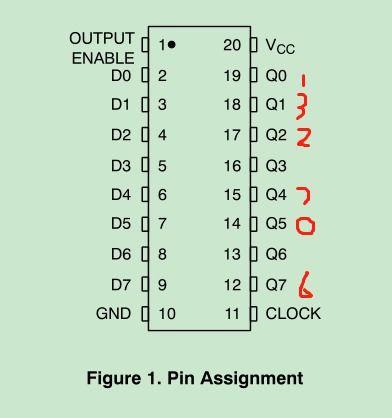

1.3 38译码器的引脚功能说明

典型的38译码器芯片拥有16个引脚。了解每个引脚的功能至关重要。

三个输入引脚通常标记为A0、A1、A2。它们接收二进制编码的输入信号,组合范围从000到111。八个输出引脚标记为Y0到Y7,对应八种可能的输入状态。正常情况下,只有一个输出引脚处于有效状态,其他都保持无效。

使能端引脚值得特别关注。大多数38译码器配备两个或三个使能端,用于控制芯片的工作状态。当使能端信号不满足条件时,所有输出都保持无效状态。这种设计便于多个译码器的级联使用。

电源引脚提供工作电压,接地引脚完成电流回路。合理的引脚布局考虑了实际使用场景,使电路连接更加直观。

1.4 38译码器的真值表分析

真值表是理解38译码器行为的最佳工具。它清晰地展示了输入输出之间的对应关系。

当输入为000时,只有Y0输出有效;输入为001时,Y1输出有效,依此类推直到输入111对应Y7有效。这种一一对应的关系确保了译码的准确性。

使能端的状态直接影响译码器工作。只有当所有使能端都满足激活条件时,译码功能才会正常执行。否则所有输出都保持无效状态,这种特性在实际应用中非常实用。

分析真值表时可以发现一个有趣的现象:任何时候最多只有一个输出有效。这种互斥特性避免了信号冲突,保证了系统的稳定运行。理解这个特性对正确使用38译码器很有帮助。

2.1 输入信号与输出信号的对应关系

38译码器的核心魅力在于它简洁的映射逻辑。三个输入引脚A0、A1、A2组成八种可能的二进制组合,每种组合唯一对应一个输出引脚的有效状态。

输入从000到111的变化,依次激活Y0到Y7的输出。这种对应关系就像精确的钥匙与锁的匹配——特定的输入组合只能打开对应的输出通道。当A2A1A0=010时,只有Y2引脚会响应;当输入变为101时,立即切换到Y5输出有效。

我曾在调试一个项目时深刻体会到这种对应关系的重要性。某个设备始终无法被选中,最终发现是输入线路上存在轻微干扰,导致实际输入信号与预期存在偏差。这种一对一的严格映射虽然精确,但也对信号质量提出了较高要求。

2.2 使能端的作用与控制逻辑

使能端是38译码器的“总开关”。通常包含两个使能引脚:一个高电平有效,一个低电平有效。只有当两个使能条件同时满足时,译码器才会进入工作状态。

以常见的74LS138为例,E1、E2、E3三个使能端需要满足特定电平组合。E1和E2必须为低电平,E3必须为高电平。任何偏离这个组合的情况都会导致所有输出保持无效状态。

这种设计提供了灵活的控制能力。你可以通过使能端轻松实现多个译码器的级联,或者将译码器纳入更大的控制系统中。使能端的存在让38译码器从单纯的信号转换器升级为可控的逻辑分配单元。

2.3 内部逻辑门电路实现原理

深入38译码器内部,你会发现一个由与门、非门构成的精巧网络。每个输出引脚都连接到一个三输入与门,而这些与门的输入则来自输入信号及其反相的组合。

具体来说,Y0对应A2'A1'A0'(“'”表示取反),Y1对应A2'A1'A0,依此类推直到Y7对应A2A1A0。每个输出通道的逻辑表达式都是三个输入变量的最小项。

这种实现方式确保了输出的互斥性。任何时候,八个与门中最多只有一个能够满足导通条件。内部的门电路经过优化布局,信号传输路径基本等长,保证了各输出通道的响应时间一致性。

2.4 工作波形与时序分析

观察38译码器的工作波形能揭示其动态特性。输入信号变化到输出响应稳定存在一个微小但关键的延迟时间——传输延迟。

这个延迟主要来自内部逻辑门的开关时间。当输入信号发生变化时,信号需要经过缓冲、反相、与运算等多个环节,每个环节都会引入一定延迟。典型值在几纳秒到几十纳秒之间,具体取决于芯片工艺和工作电压。

时序分析时需要特别注意竞争冒险现象。当多个输入信号同时变化时,可能产生短暂的错误输出。在实际应用中,通常通过控制信号变化顺序或添加滤波电路来避免这个问题。理解这些时序特性对设计稳定可靠的数字系统至关重要。

3.1 地址译码与存储器扩展

38译码器在存储器系统中扮演着地址分配的关键角色。三个输入引脚可以区分八个不同的存储单元或外设地址,这种能力让它在小型存储系统中特别实用。

想象一个需要连接八片存储芯片的系统。每片芯片都有自己的片选信号,而38译码器正好能提供这八个独立的使能信号。输入地址的高三位接入译码器,产生的八个输出分别连接到不同存储芯片的片选端。当地址变化时,只有一个存储芯片被激活,其余保持休眠状态。

我参与过一个嵌入式项目,使用38译码器扩展外部存储器。原本有限的地址空间通过译码器划分成了八个独立区域,分别对应不同的功能模块。这种设计不仅节省了微控制器的IO资源,还让系统架构更加清晰。

3.2 数据选择与多路分配

在数据通路设计中,38译码器经常用作多路分配器。它能够将单一数据源根据选择信号分配到八个不同目的地,这种功能在总线系统中极为重要。

工作模式很直观:使能端接数据信号,三个地址输入端作为选择信号。当特定地址组合出现时,对应的输出引脚会复制输入数据的电平状态。其他输出则保持无效电平,确保数据只送达预定目标。

这种应用在通信接口中很常见。比如一个主设备需要与多个从设备通信,通过38译码器就能实现精准的目标选择。每个从设备连接到不同的输出引脚,主设备通过改变地址来选择通信对象。

3.3 数字显示系统中的应用

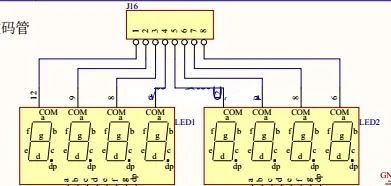

七段数码管驱动是38译码器的经典应用场景。虽然需要配合其他电路,但译码器在这里承担着显示内容选择的重要任务。

实际应用中,38译码器的输出通常连接到驱动电路,再驱动数码管的各个段。通过精心设计输入编码,可以实现数字0-7的显示。每个数字对应特定的输入组合,译码器输出激活相应的显示段组合。

记得我第一次用38译码器做数码管显示实验时,那种从二进制输入到直观数字显示的转换过程让人印象深刻。虽然现在有更集化的显示驱动芯片,但理解这种基础原理对深入掌握数字系统设计很有帮助。

3.4 控制系统中的逻辑分配

工业控制和自动化系统中,38译码器经常承担逻辑信号分配的任务。它将紧凑的控制编码展开为多个独立的控制信号,简化了系统布线。

典型应用包括多路继电器控制、步进电机相序生成、或者多路阀门的开关控制。控制器只需要输出三位编码,就能精确控制八个执行机构中的一个。这种设计大幅减少了控制线的数量,特别是在远距离控制场合优势明显。

在复杂的控制逻辑中,多个38译码器可以协同工作。一个译码器的输出作为另一个译码器的使能信号,形成层次化的控制结构。这种级联方式能够扩展控制范围,同时保持系统的模块化特性。

4.1 多级译码器的级联实现

单个38译码器只能处理三位输入,产生八个输出。实际工程中经常需要更大的译码范围,这时级联多个译码器成为必然选择。

级联的核心思路很巧妙:将低位译码器的输出作为高位译码器的使能信号。比如两个38译码器级联,第一个译码器的八个输出分别控制第二个译码器的使能端。这样六位输入地址就能产生六十四个独立输出,扩展效果非常显著。

我设计过一个需要三十二路输出的系统,采用四级级联结构。每增加一级译码器,输出数量就乘以八。这种指数级增长让系统扩展变得相对容易,虽然延时也会相应增加。

级联时需要注意使能信号的连接顺序。通常高位地址控制第一级译码,低位地址控制后续级别。这种安排符合地址空间的自然划分,也便于后续的故障排查。

4.2 38译码器的性能参数分析

评估译码器性能时,传播延时是最关键的指标。从输入变化到输出稳定的这段时间,直接影响整个系统的工作频率。

典型38译码器的传播延时在十几纳秒量级。这个数值看似很小,但在高速系统中可能成为瓶颈。级联多个译码器时,总延时近似等于各级延时之和。我在一个百兆赫兹系统中就遇到过这个问题,不得不改用更快的译码器型号。

功耗是另一个重要考量。静态功耗通常很低,但开关过程中的动态功耗不容忽视。输出负载电容越大,切换时的电流峰值越高。适当增加输出缓冲可以改善驱动能力,但会牺牲一些速度。

噪声容限和扇出能力决定了译码器的驱动稳定性。标准TTL电平的38译码器能驱动十个左右同类负载,超过这个数量就需要额外的缓冲电路。

4.3 实际应用中的注意事项

PCB布局对译码器性能影响很大。输入信号线要尽量等长,避免时序偏差。输出线如果较长,最好串接小电阻来抑制信号反射。

电源去耦必须认真对待。每个译码器芯片的电源引脚附近都应该放置一个0.1μF的陶瓷电容。高频应用中,还需要并联一个更小的电容来滤除高频噪声。

未使用的输入引脚不能悬空。TTL电路中悬空输入可能被误读为高电平,导致意外动作。所有不用的输入都应该接到固定的高电平或低电平,具体接法参考器件手册。

温度对性能的影响经常被忽视。商业级芯片的工作温度范围是0-70℃,工业级能达到-40到85℃。在恶劣环境中要留出足够的性能余量,避免高温下出现时序问题。

4.4 与其他类型译码器的对比

24译码器结构更简单,但输出数量只有四个。在只需要少量输出的场合,它的成本和功耗优势明显。不过扩展性不如38译码器,级联效率也较低。

416译码器能直接处理四位输入,产生十六个输出。集成度更高,但引脚数量增多,封装尺寸更大。在空间受限的设计中可能不太适用,而且价格通常更高。

BCD到七段译码器是专用器件,内部集成了编码转换逻辑。显示应用中比通用38译码器更方便,但灵活性受限,不能用于其他译码场合。

各种译码器各有优劣,选择时要综合考虑输出数量、速度要求、成本预算和板卡空间。38译码器在复杂度与功能之间找到了不错的平衡点,这或许是它在教学中如此受欢迎的原因之一。